Bạn làm trong ngành điện tử? Bạn cần tìm hiểu rõ về cổng Logic? Vâng bạn hãy xem chi tiết về cổng Logic trong bài viết này bạn nhé.

Khái niệm các cổng logic

Cổng logic (tiếng Anh gọi là: logic gate) là thuật ngữ trong điện tử học dùng để chỉ mạch điện thực hiện một hàm Boole lý tưởng hóa. Nghĩa là, nó thực hiện một phép toán logic trên một hoặc nhiều logic đầu vào, đồng thời tạo ra một kết quả logic ra duy nhất, với thời gian thực hiện lý tưởng hóa là không có trễ.

Các đại lượng nhị phân trong thực tế là những đại lượng Vật lý khác nhau (như dòng điện, điện áp,…). Những đại lượng này có thể thể hiện bằng hai trạng thái có ‘1’ hoặc không ’0’.

Các cổng logic là các phần tử đóng vai trò chính để thực hiện các chức năng logic đơn giản nhất trong các sơ đồ logic nhằm thực hiện một hàm logic nào đó. Quan hệ logic cơ bản nhất có ba loại: AND, OR, NOT. Cổng logic gồm các phần tử có nhiều đầu vào và chỉ có duy nhất một đầu ra. Đầu ra là tổ hợp của nhiều đầu vào. Từ các cổng logic ta có thể kết hợp lại để tạo ra nhiều mạch logic thực hiện các hàm logic phức tạp hơn.

Bảng chân lý (Bảng sự thật)

Dùng để mô tả đáp ứng của mạch tại ngõ ra đối với các tổ hợp mức logic khác nhau tại các ngõ vào. Mức logic tại các ngõ vào/ra chỉ nhận một trong hai giá trị là 0 hoặc 1. Với mạch logic có N ngõ vào thì sẽ có 2N tổ hợp hoặc trạng thái của ngõ ra. Dưới đây là một số hình ảnh:

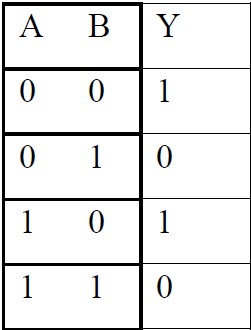

- Mạch logic 2 ngõ vào, 1 ngõ ra:

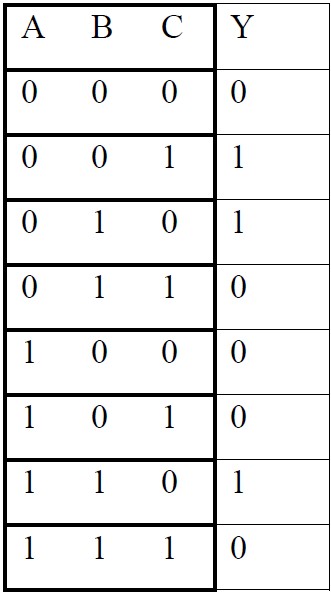

- Mạch logic 3 ngõ vào, 1 ngõ ra:

Phân loại các cổng logic

Quy định về mức 0 và mức 1 như sau:

- Nếu IC của TTL thì điện áp vào là 5V, lúc này ta có mức 1 = 5V và mức 0 là = 0V.

- Nếu IC của CMOS thì điện áp vào Vdd = 3V – 18V nên mức 1 = Vdd và mức 0 vẫn là = 0V.

Các cổng logic cơ sở

Cổng OR (HOẶC)

Cổng HOẶC sẽ có 2 hoặc nhiều lối vào nhưng chỉ có một lối ra. Lối ra ở mức 1 khi có ít nhất một lối vào ở mức 1 (Lối ra sẽ có tín hiệu khi một lối vào có tín hiệu). Ta có bảng chân lý dưới đây:

Ta sẽ viết Y = A + B và nói cổng HOẶC thực hiện phép cộng logic.

Ta có nhận xét:

Y = 0 nếu tất cả các biến vào đều bằng 0

Y = 1 nếu có ít nhất một biến vào bằng 1

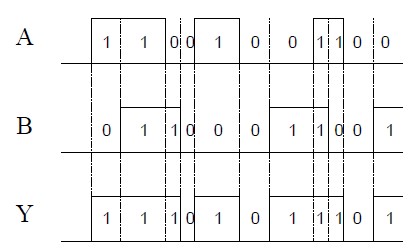

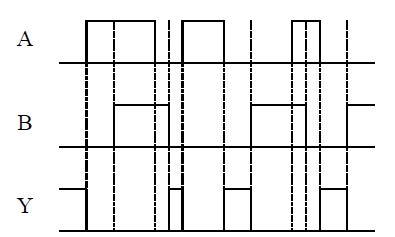

Dưới đây là giản đồ xung:

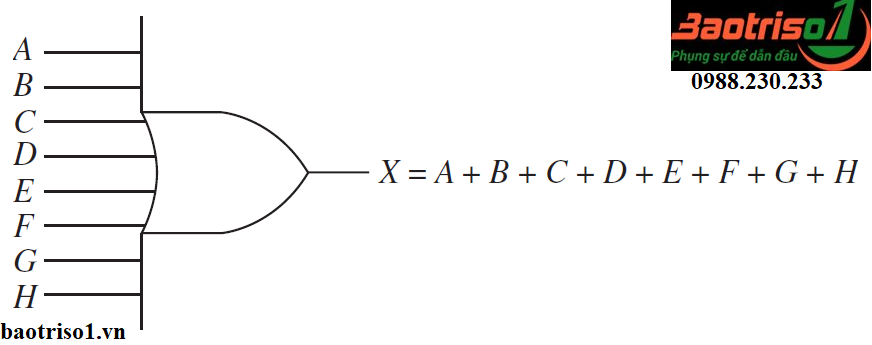

Với trường hợp tổng quát cổng OR có nhiều biến vào độc lập

Có thể xem cổng HOẶC như một mạch điện mắc song song như hình sau:

Trong mạch điện, ta nhận thấy chỉ cần một chuyển mạch A, B hoặc C đóng, thì đèn sẽ sáng ngay.

Cổng logic OR thực hiện quan hệ: một sự kiện sẽ xảy ra khi chỉ cần có một điều kiện quyết định sự kiện đó được đáp ứng.

Cổng AND (VÀ)

Đối với cổng VÀ có 2 hoặc nhiều lối vào và chỉ có một lối ra. Lối ra chỉ ở mức 1 khi tất cả lối vào đều ở mức 1 (Lối ra có tín hiệu nếu tất cả lối vào đều có tín hiệu).

Ta sẽ viết Y = AB và nói cổng VÀ thực hiện phép nhân logic

Ta có nhận xét:

Y = 0 chỉ khi có ít nhất một biến vào bằng 0

Y = 1 chỉ khi tất cả các biến vào đều bằng 1

Giản đồ xung:

Trường hợp tổng quát cổng AND có nhiều biến vào độc lập như sau:

Có thể xem cổng AND như một mạch điện mắc nối tiếp:

Trong mạch điện, ta nhận thấy khi tất cả các chuyển mạch A, B, C đều đóng thì đèn mới sáng được.

Cổng logic AND thực hiện quan hệ: một sự kiện sẽ xảy ra chỉ khi tất cả mọi điều kiện quyết định sự kiện đó được đáp ứng.

Cổng NO (KHÔNG)

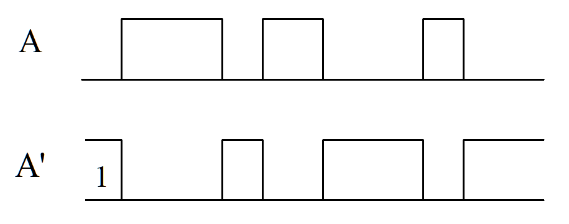

Cổng KHÔNG còn gọi là cổng đảo hoặc cổng chặn. Nó chỉ có một lối vào và một lối ra và là cổng thực hiện phép phủ định logic.

Giản đồ xung:

Các cổng logic ghép

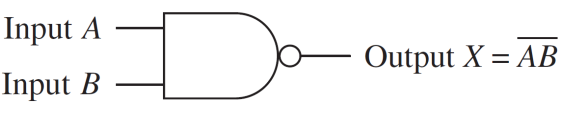

Cổng NAND (KHÔNG VÀ)

Cổng KHÔNG VÀ chính là cổng VÀ bị phủ định. Biểu diễn như sau:

![]()

Dưới đây là bảng sự thật với hàm NAND 2 biến:

Nhận xét:

Y = 0 nếu tất cả các biến vào đều bằng 1

Y = 1 nếu có ít nhất một biến vào bằng 0

Giản đồ xung:

Trong trường hợp tổng quát cổng NAND có nhiều biến vào độc lập

Cổng NOR (KHÔNG HOẶC)

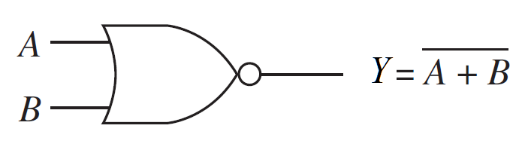

Cổng KHÔNG HOẶC chính là cổng HOẶC bị phủ định. Biểu diễn như sau:

![]()

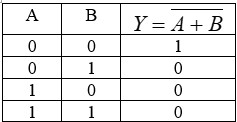

Bảng sự thật với hàm NOR 2 biến như sau:

Ta có nhận xét:

Y = 0 nếu có ít nhất một biến vào bằng 1

Y = 1nếu tất cả các biến vào đều bằng 0

Giản đồ xung:

Với trường hợp tổng quát cổng NOR có nhiều biến vào độc lập

Cổng khác dấu

-

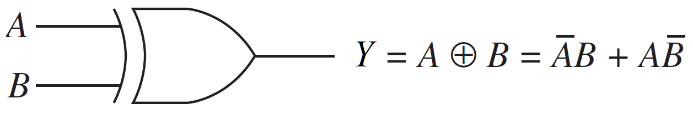

Cổng Exclusive OR (HOẶC loại trừ)

Cổng hoặc loại trừ hay còn gọi là cổng cộng modul 2 hoặc là cộng không nhớ, được gọi tắt là EX-OR. Có biểu thức logic như sau:

![]()

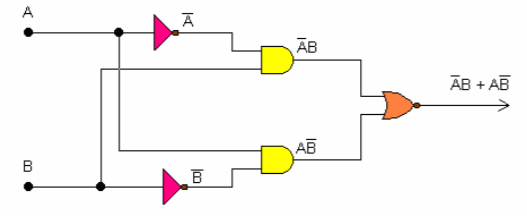

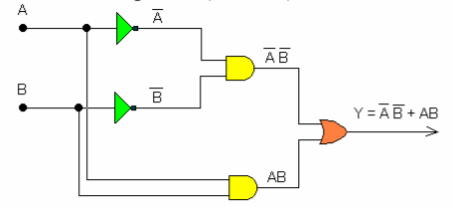

Ta có sơ đồ mạch như hình dưới:

![]()

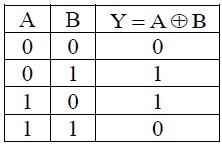

Dưới đây là bảng sự thật với hàm EX-OR 2 biến:

Ta có nhận xét:

Y = 0 : chỉ khi cả hai biến vào có giá trị giống nhau

Y = 1 : chỉ khi cả hai biến vào có giá trị khác nhau

So sánh với cổng logic OR, ta nhận thấy 3 trạng thái đầu là của cổng logic OR chỉ khác ở trạng thái thứ tư, ta gọi là cổng logic KHÔNG đồng trị hay là HOẶC loại trừ (Exclusive OR), có ký hiệu như sau:

Đầu ra của cổng EX-OR bằng 1 khi hai đầu vào khác trạng thái và bằng 0 khi hai đầu vào cùng trạng thái. Nếu nhiều đầu vào thì đầu ra bằng 1 khi số bit 1 ở đầu vào là số lẻ và bằng 0 khi số bit 1 ở đầu vào là số chẵn.

Chú ý: Cổng EX-OR chỉ có 2 ngõ vào.

Giản đồ xung:

-

Cổng Exclusive NOR (không hoặc loại trừ)

Một cổng logic khác cũng thường được sử dụng đó là cổng Exclusive NOR (EX-NOR) hay còn gọi là cổng đồng dấu. Biểu diễn như sau:

![]()

Hình dưới là mạch logic để thực hiện hàm logic ở trên:

Bảng sự thật với hàm EX-NOR 2 biến là:

Ta nhận xét:

Y = 0 : chỉ khi cả hai biến vào có giá trị khác nhau

Y = 1 : chỉ khi cả hai biến vào có giá trị giống nhau

- Cổng EX-NOR logic:

Chú ý: Cổng EX-NOR chỉ có 2 ngõ vào.

Giản đồ xung:

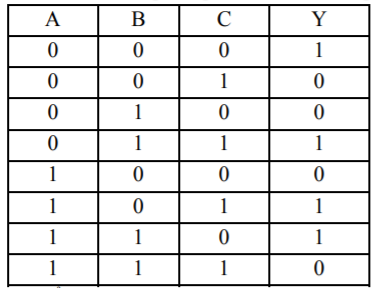

Đầu ra của cổng EX-NOR bằng 1 chỉ khi hai đầu vào cùng trạng thái và bằng 0 chỉ khi khác trạng thái. Nếu có nhiều đầu vào thì đầu ra sẽ bằng 1 nếu số bit 0 ở đầu vào là số lẻ và bằng 0 nếu số bit 0 ở đầu vào là số chẵn. Ví dụ: bảng trạng thái của một cổng EX-NOR 3 đầu vào như sau:

Người ta thường dùng các cổng EX-OR và EX-NOR trong các bộ so sánh, bộ cộng,…

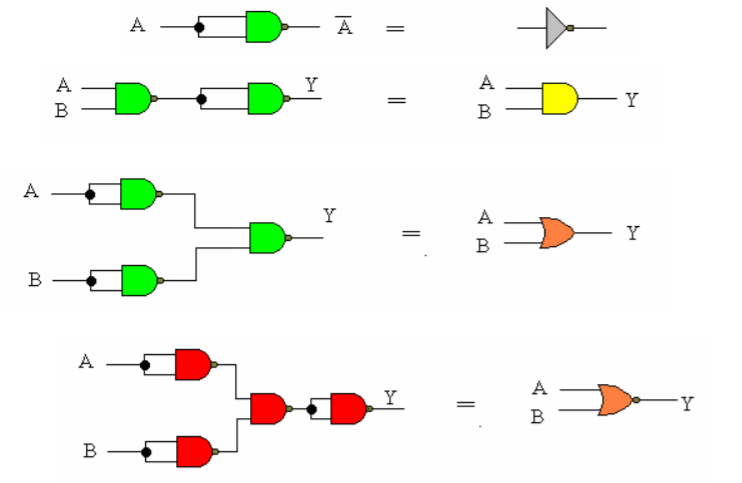

Trong các cổng nói trên, hai cổng NAND và NOR được dùng khá linh hoạt. Từ hai cổng này, người ta có thể tạo ra các cổng logic cơ bản NO, AND, OR

- Sử dụng các cổng NAND:

- Sử dụng các cổng NOR:

Cổng logic 3 trạng thái TS (three state)

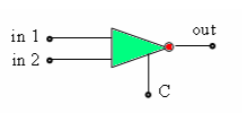

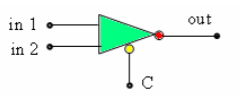

Cổng logic ba trạng thái là cổng logic mà đầu ra có thêm trạng thái thứ ba, trạng thái này gọi là trạng thái treo ngoài hai trạng thái 1 và 0. Đầu ra Y có thể nằm ở một trong ba trạng thái sau đây:

Trạng thái mức cao, trạng thái mức thấp 1 hoặc 0. Trạng thái thứ ba là trạng thái treo hay nói cách khác là trạng thái tổng trở cao. Lúc này đầu ra Y tách ra khỏi hệ thống.

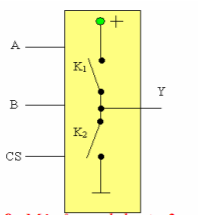

Mô tả mạch logic 3 trạng thái như sau:

Khi K1 đóng thì đầu ra có trạng thái 0. Khi K1, K2 cùng đóng, thì đầu ra có trạng thái 1. Khi K1, K2 cùng tắt, lúc này mạch ở trạng thái thứ 3 tổng trở cao, đầu ra Y tách khỏi mạch (dù thực tế nó vẫn nối với mạch. CS (Chip Select) dùng để chọn chip. CS điều khiển mạch ở trạng thái thứ ba. Khi CS = 1 (hoặc 0) thì hai khóa đều mở, nó độc lập với tín hiệu vào A, B.

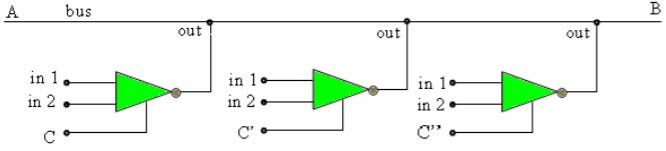

Cổng logic 3 trạng thái được sử dụng trong trường hợp cần ghép kênh các tín hiệu cần truyền luân lưu trên một dây dẫn AB (AB còn gọi là bus).

- Khi trạng thái treo ở mức thấp:

- Khi trạng thái treo ở mức cao:

Ưu điểm nổi bật của các vi mạch logic ba trạng thái chính là có thể nối đầu ra của vi mạch lên cùng một kênh truyền chung. Điều này tạo nên sự đơn giản rất nhiều cho việc tạo lập kênh truyền số liệu trong một hệ thống logic. Thí dụ về việc nối vi mạch logic trên một kênh truyền:

Khi tín hiệu điều khiển C, C’ , C’’ có thứ tự thời gian ở mức cao, thì các tín hiệu dữ liệu ở ba nhóm đầu vào sau khi đã thực hiện quan hệ logic sẽ đưa ra bus luân lưu theo thứ tự thời gian tương ứng. Để các cổng TS được hoạt động bình thường thì tại một thời điểm bất kỳ chỉ cho phép một cổng duy nhất ở trạng thái công tác. Nếu không sẽ xảy ra trường hợp một lúc có đến hai đầu ra của cổng cùng thông với bus, nếu hai cổng này có đầu ra khác trạng thái nhau, một cổng ở mức cao, một cổng ở mức thấp sẽ dẫn đến hỏng cổng.

Ứng dụng của các cổng logic

Các cổng logic có ứng dụng chủ yếu được xác định dựa trên bảng trạng thái của chúng, tức là phương thức hoạt động của chúng. Các cổng logic cơ bản được sử dụng nhiều trong mạch điện như khóa nút nhấn, kích hoạt báo trộm bằng ánh sáng, bộ điều chỉnh nhiệt độ, hệ thống tưới nước tự động, v.v.

Ngoài ra, cổng logic cũng chính là các phần tử cấu thành nên các mạch tổ hợp như mạch giải mã, mạch mã hóa, mạch đa hợp, mạch giải đa hợp,…